- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX11202BEUB+T (Maxim Integrated Products)IC ADC 24BIT SRL 13.75SPS 10UMAX

12

Maxim Integrated

24-Bit, Single-Channel, Ultra-Low-Power, Delta

Sigma ADC with 2-Wire Serial Interface

MAX11202

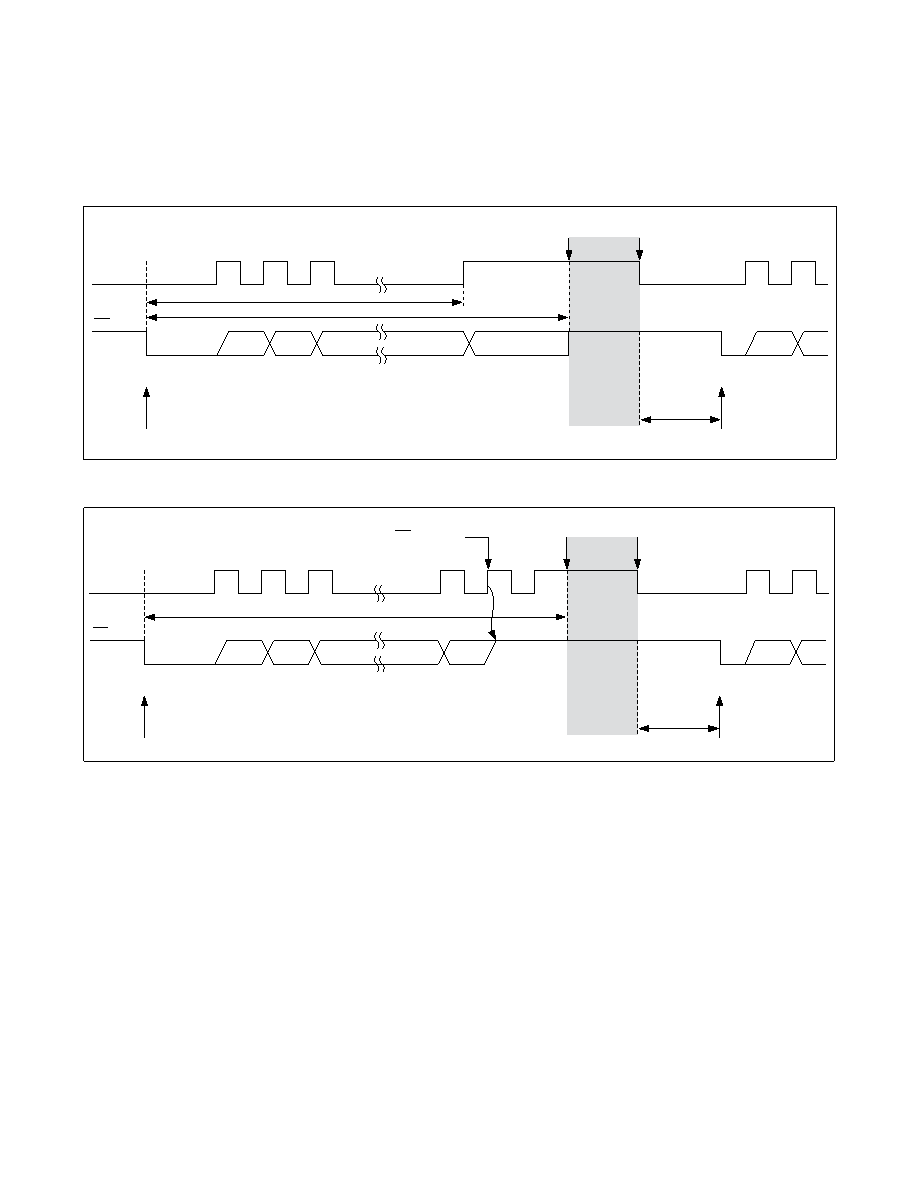

Figure 5. Timing Diagram for Sleep Mode Activation Followed by Self-Calibration at Wake-Up

Figure 4. Timing Diagram for Data Read Followed by Sleep Mode Activation; Single Conversion Timing

SLEEP

MODE

12

3

24

25

26

CONVERSION IS DONE

DATA IS AVAILABLE

t12

t10

DEVICE ENTERS

SLEEP MODE

DEVICE EXITS OUT SLEEP MODE

AND STARTS CALIBRATION

D0

RDY/DOUT

D23

D22

D23

D22

SCLK

CONVERSION IS DONE

DATA IS AVAILABLE AFTER CALIBRATION

25TH SCLK PULLS RDY/DOUT HIGH

SLEEP

MODE

12

3

24

CONVERSION IS DONE

DATA IS AVAILABLE

t9

t11

t10

DEVICE ENTERS

SLEEP MODE

DEVICE EXITS OUT

SLEEP MODE

D0

RDY/DOUT

D23

D22

D23

D22

SCLK

CONVERSION IS DONE

DATA IS AVAILABLE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX11210EEE+T

ADC 24BIT 4WIRE SPI 16-QSOP

MAX11212BEUB+T

IC ADC 18BIT SRL 13.75SPS 10UMAX

MAX1135BCAP+

IC ADC 16BIT 150KSPS 20-SSOP

MAX1138LEEE+T

IC ADC 10BIT SERIAL 16-QSOP

MAX1159AEUI+

IC ADC 14BIT 135KSPS 28-TSSOP

MAX11602EEE+

IC ADC SERIAL 8BIT 8CH 16-QSOP

MAX11610EEE+T

IC ADC SERIAL 10BIT 12CH 16-QSOP

MAX11616EEE+T

IC ADC SERIAL 12BIT 12CH 16-QSOP

相关代理商/技术参数

MAX11202EUB+

功能描述:模数转换器 - ADC 24 Bit Sigma Delta ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11202EUB+T

功能描述:模数转换器 - ADC 24 Bit Sigma Delta ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11203

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:16-Bit, Single-Channel, Ultra-Low-Power, Delta-Sigma ADCs with Programmable Gain and GPIO

MAX11203EEE+

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11203EEE+T

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11205

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:16-Bit, Single-Channel, Ultra-Low Power, Delta-Sigma ADC with 2-Wire Serial Interface

MAX11205AEUB+

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11205AEUB+T

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32